- #VERILOG TEST BENCH EXAMPLE GENERATOR#

- #VERILOG TEST BENCH EXAMPLE DRIVER#

- #VERILOG TEST BENCH EXAMPLE VERIFICATION#

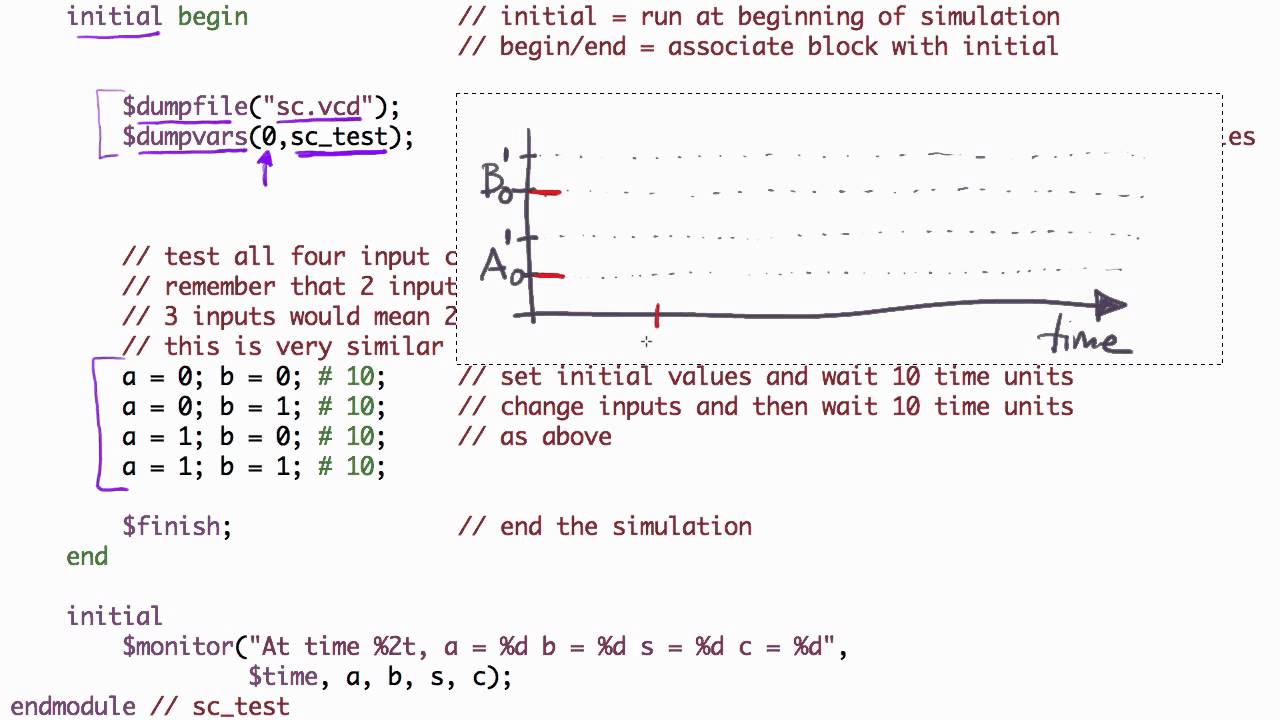

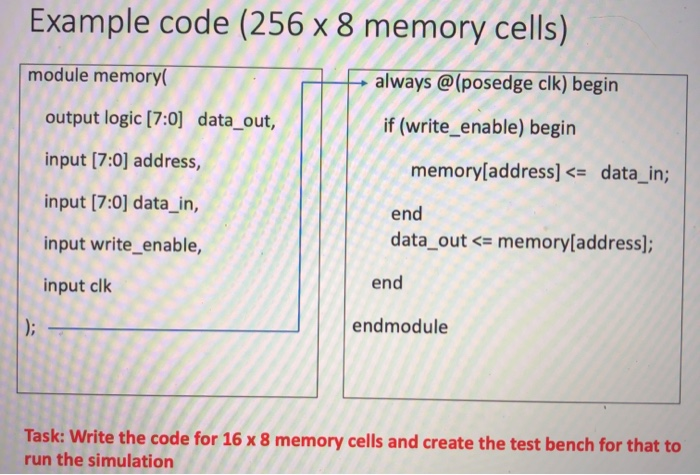

#VERILOG TEST BENCH EXAMPLE DRIVER#

It is the job of the driver to get the data object and translate it into something the DUT can understand. Data transactions are implemented as class objects shown by the blue squares in the image above.

#VERILOG TEST BENCH EXAMPLE GENERATOR#

The driver can then simply drive the data provided to it by the generator through the interface.

#VERILOG TEST BENCH EXAMPLE VERIFICATION#

The generator is a verification component that can create valid data transactions and send them to the driver. In the future, if the interface changed, then the new driver can call the same task and drive signals in a different way.

This is the level of abstraction required to make testbenches more flexible and scalable. The timing information is defined within the task provided by the interface. When the driver has to drive some input values to the design, it simply has to call this pre-defined task in the interface, without actually knowing the timing relation between these signals.

The driver is the verification component that does the pin-wiggling of the DUT, through a task defined in the interface. The design can then be driven with values through this interface. Instead, we can place all the design input-output ports into a container which becomes an interface to the DUT. If the design contained hundreds of port signals it would be cumbersome to connect, maintain and re-use those signals. Develop rest of the testbench and write stimulus that can be driven to the designĬlick here for a complete SystemVerilog testbench example ! What is an interface ? Instantiate the design module and connect the variables declared above the design as inputs because they are connected with the ports in the design These variables are assigned some values that in turn gets transferred to Declare variables that need to be connected to the design instance All verification components are placed in this top testbench module In pre validation, it is also called as Design Under Verification, DUV in short. DUT is a term typically used in post validation of the silicon once the chip is fabricated. Monitor the design input-output ports to capture design activityĬhecks output from the design with expected behaviorĬontains all the verification components mentioned aboveĬontains the environment that can be tweaked with different configuration settingsĭUT stands for Design Under Test and is the hardware design written in Verilog or VHDL. Generates different input stimulus to be driven to DUTĬontains design signals that can be driven or monitoredĭrives the generated stimulus to the design Let's take a look at a simple testbench and try to understand about the various components that facilitate data transfer from and to the DUT. The example shown in Introduction is not modular, scalable, flexible or even re-usable because of the way DUT is connected, and how signals are driven.

We need to have an environment known as a testbench to run any kind of simulation on the design.Ĭlick here to refresh basic concepts of a simulation What is the purpose of a testbench ?Ī testbench allows us to verify the functionality of a design through simulations.

0 kommentar(er)

0 kommentar(er)